Se consideră circuitul din figura următoare 2.1 pentru care se vor face câteva consideraţii legate de efectul întârzierilor de propagare ale semnalelor logice prin porţi logice cascadate.

Figura 2.1 Exemplu de propagare a unui semnal logic

şi reprezentarea unei porţi NAND afectată de întârziere

Ieşirea circuitului din figura 2.1 (stânga) nu poate fi descrisă numai cu ajutorul variabilelor de intrare. În expresia funcţiei de ieşire va interveni şi timpul, având în vedere că un circuit NAND real poate fi reprezentat ca în figura 2.1 (dreapta), unde D este un circuit de întârziere (cu timpul tp).

Ţinând cont de acest aspect, circuitul se poate redesena ca în figura 2.2.

Figura 2.2 Modelarea întârzierii introdusă de structuri logice

y(t) = y’ (t-2tp)

iar cu 2tp = d, relaţia se poate scrie sub forma (2.1)

y’ (t) = y (t + d)

S-a considerat că x0, x1, x2 nu se modifică în acest interval.

Dacă împărţim timpul în intervale d şi notăm an= a(nd), putem scrie:

Dacă împărţim timpul în intervale d şi notăm an= a(nd), putem scrie:

(2.2)

Se va numi, în continuare, variabila y – variabilă secundară internă sau variabilă de stare, având în vedere că ea descrie starea atinsă de circuit la un moment dat. Circuitul de mai sus prezintă o singură buclă de reacţie.

În continuare, se consideră un circuit cu mai multe bucle de reacţie, ca cel din figura 2.3:

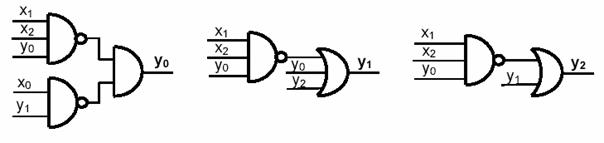

Figura 2.3 Circuit logic cu mai multe bucle

Procedând ca mai sus, se identifică buclele circuitului, introducând înaintea fiecărei variabile de stare propusă câte un circuit de întârziere. Se pot astfel scrie relaţiile (2.3)

Figura 2.4 Evidenţierea întârzierilor într-un circuit combinaţional

cu mai multe bucle

(2.3)

Corespunzător ecuaţiilor (2.3), în figura 2.5 sunt reprezentate circuitele ce definesc variabilele de stare, iar în figura 2.6 circuitele de ieşire.

Figura 2.5 Implementarea variabilelor de stare

Figura 2.6 Implementarea variabilelor de ieşire

În cazul general, dacă se consideră un sistem cu bucle de reacţie cu k intrări şi m ieşiri, trebuie introduse p variabile de stare pentru a putea defini toate ieşirile într-un manieră combinaţională. Astfel, se introduc p întârzieri fictive d în schemă. Trebuie studiată evoluţia sistemului după fiecare eşantion de timp d. Dacă xin, yjn şi zln sunt valorile intrărilor, variabilelor de stare, respectiv ieşirilor la momentul de timp nd, atunci se pot scrie relaţiile (2.4) :

(2.4)

Un sistem a cărui funcţionare este descrisă de astfel de ecuaţii se numeşte sistem secvenţial sau automat finit.

Un automat finit este deci un cvintuplu A = (X, Y, Z, f, g), unde X, Y, Z sunt mulţimi nevide, iar f şi g sunt funcţii definite pe aceste mulţimi.

Un automat finit este deci un cvintuplu A = (X, Y, Z, f, g), unde X, Y, Z sunt mulţimi nevide, iar f şi g sunt funcţii definite pe aceste mulţimi.

X - mulţimea semnalelor de intrare (alfabet de intrare)

Y - mulţimea stărilor mulţimi finite

Z - mulţimea semnalelor de ieşire (alfabet de ieşire)

f : X × Y →Y – funcţie de tranziţie

g : X × Y→ Z – funcţie de ieşire

Un automat care răspunde acestor cerinţe se numeşte automat Mealey şi are structura prezentată în figura 2.7. Ecuaţiile sale de funcţionare sunt de forma (2.5).

Figura 2.7 Automat Mealey

(2.5)

Dacă Y=Æ Þ f: X x Æ → Æ atunci nu este definibilă noţiunea de stare, iar g: X x Æ → Z devine g: X→ Z.

Acest caz particular defineşte circuitele combinaţionale (care se mai numesc dealtfel şi automate triviale sau automate combinative); ieşirile acestora sunt complet determinate la orice moment de timp numai de intrări.

Un alt caz particular este g, adică automatul de tip Moore g: Y→ Z.

La automatele de tip Mealey, ieşirile sunt definite în timpul tranziţiilor dintre stări, în timp ce la automatele Moore, ieşirile sunt definite la atingerea stărilor. Pentru realizarea fizică a acestor structuri, se folosesc circuite combinaţionale pentru implementarea funcţiilor f şi g şi elemente de memorare pentru implementarea circuitelor de întârziere.